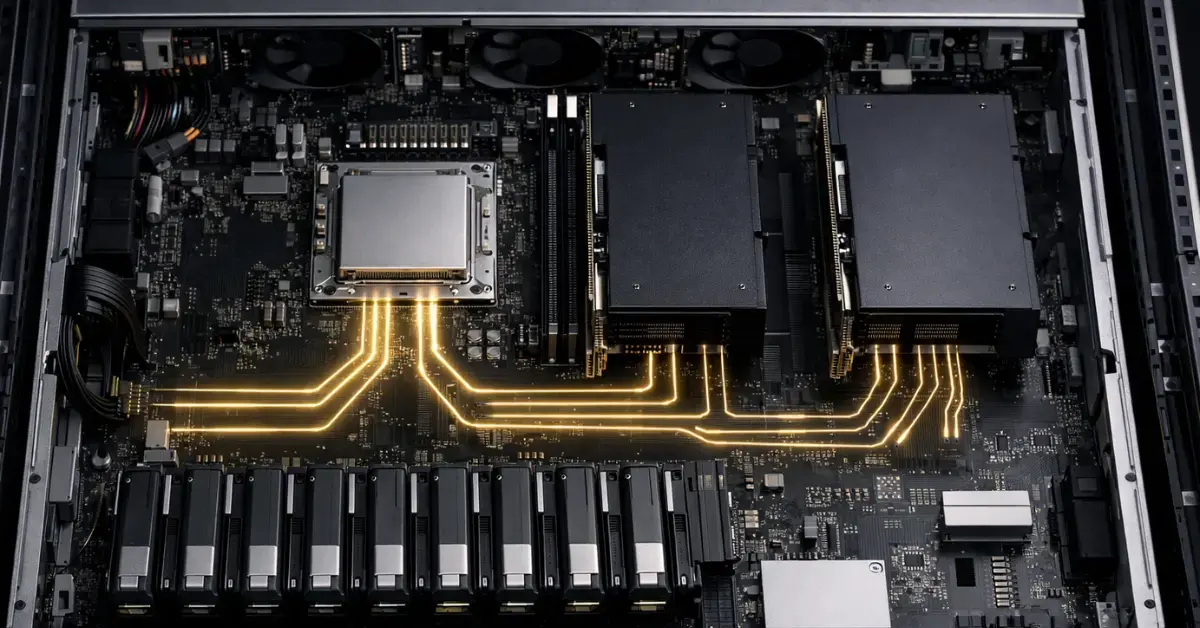

В серверных конфигурациях с GPU и NVMe «PCIe линии» — это не абстрактная характеристика из спецификации, а реальный ресурс, который определяет, сколько устройств вы подключите без потерь скорости, как предсказуемо будет масштабироваться система и насколько легко вы сможете её расширять. Ошибка в планировании PCIe редко даёт «минус 10%» — чаще она превращается в цепочку последствий: GPU внезапно работают в x8 вместо x16, часть NVMe уходит «через чипсет» и упирается в аплинк, а при добавлении ещё одной карты всё начинает деградировать непонятно почему.

Типичная история: купили сервер под 4×GPU + NVMe под датасет, всё «по слотам» выглядит идеально, но на практике один райзер висит на свитче с оверсабскрипшеном, два слота делят один x16, половина U.2/EDSFF идёт через PCH, а в BIOS включены настройки, которые режут peer-to-peer или принудительно «роняют» линк. В итоге вы получаете дорогую систему, которая ведёт себя как более дешёвая — и это почти всегда лечится на этапе выбора платформы и топологии, а не после поставки. Ничего не понятно? Давайте разберёмся вместе.

PCIe инженерно точно: Gen, ширина, линии, реальная пропускная способность

PCIe lane (линия) — это пара высокоскоростных дифференциальных каналов «туда» и «обратно». Важно: PCIe является full-duplex интерфейсом — при нормальной работе передача может идти одновременно в обе стороны.

Link width (ширина линка) — это количество линий, объединённых в один линк: x1 / x4 / x8 / x16. Если устройство и слот физически x16, это ещё не означает, что линк реально поднимется в x16.

Поколение (PCIe Gen) задаёт скорость одной линии. Каждое новое поколение примерно удваивает пропускную способность, но в реальных системах есть нюансы:

- линк может подняться не на максимальном Gen (downtraining), если сигнал «не держится» (райзер/ретаймер/длина трасс/контакты);

- линк может подняться не в полной ширине (например, x8 вместо x16), если не хватает линий или так разведена плата.

Ключевая мысль: «слот x16» физически ≠ «линк x16» электрически.

PCIe Gen и пропускная способность (порядок величин)

| PCIe Gen | Скорость/линия (теоретическая) | Полезная пропускная способность (примерно, per direction) | Примерно x4 (per direction) | Примерно x16 (per direction) | Типичные устройства |

| Gen3 | 8 GT/s | около 1 GB/s на линию | ~4 GB/s | ~16 GB/s | NVMe (старые), NIC 25/40/100G, часть GPU/accelerators |

| Gen4 | 16 GT/s | около 2 GB/s на линию | ~8 GB/s | ~32 GB/s | NVMe Gen4, GPU PCIe, NIC 100/200G |

| Gen5 | 32 GT/s | около 4 GB/s на линию | ~16 GB/s | ~64 GB/s | NVMe Gen5, современные GPU/FPGA, NIC 200/400G |

| Gen6 | 64 GT/s | около 8 GB/s на линию | ~32 GB/s | ~128 GB/s | платформы/фабрики для AI/HPC, дисагрегация, будущие NVMe/CXL |

Практическая интерпретация: x8 Gen5 (~32 GB/s в одну сторону) часто уже сопоставим с x16 Gen4 (~32 GB/s) — но это работает только если топология, свитч/аплинк, NUMA и BIOS не ломают картину.

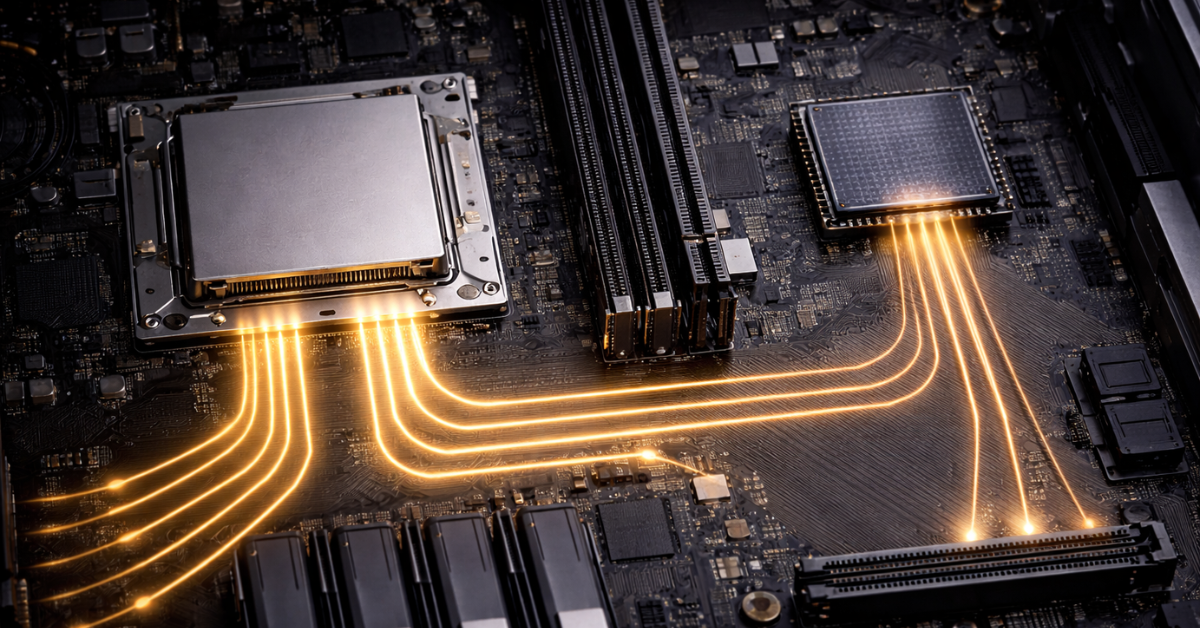

Откуда берутся линии: CPU-линии vs линии чипсета (PCH) и почему это ломает ожидания

В сервере линии PCIe «приходят» из двух мест:

- CPU PCIe lanes — самые ценные:

- минимальная задержка и максимально предсказуемая полоса;

- именно на них обычно рассчитывают для GPU, NIC 200/400G, NVMe напрямую к CPU.

- Чипсет / PCH lanes — часто «дешевле», потому что почти всегда проходят через аплинк CPU↔PCH (аналогично DMI/UPI-подобным связям в зависимости от платформы). Это означает:

- устройства делят общий канал к CPU;

- при активной нагрузке несколькими NVMe/контроллерами вы можете упереться не в «x4 каждого диска», а в узкое место аплинка.

Типовые ловушки:

- «второй M.2» или дополнительный контроллер отъедает линии у другого слота/порта;

- слотов много, но половина из них «висит» на PCH или делит один набор линий;

- часть U.2/EDSFF корзины физически выглядит как «много NVMe», но по факту агрегирована через свитч/хаб с ограниченным аплинком.

Платформенный «lane budget» — почему он меняет весь дизайн

У разных платформ радикально разный бюджет линий, и это напрямую влияет на то, насколько «честно» вы сможете подключить GPU + NVMe:

- Intel 5th Gen Xeon Scalable: заявлено до 80 линий PCIe 5.0

- AMD EPYC 9004 (Genoa/Bergamo): в материалах AMD и whitepaper фигурируют 128 линий PCIe Gen5 (в 1P-конфигурации)

Это не «маркетинг про числа»: разница между 80 и 128 линиями — это разница между «4×GPU + немного NVMe» и «4×GPU + много NVMe + быстрый NIC без компромиссов». ли необходимость уходить в свитчи и мириться с оверсабскрипшеном (переподпиской - когда устройства готовы потреблять ресурсов в виде линий, но их нет физически).

Почему PCIe критичен для GPU: не только “полоса”, но и топология

Когда полоса PCIe действительно важна для GPU

PCIe-полоса влияет на производительность GPU сильнее всего в сценариях, где данные постоянно «ездят» между CPU/памятью и GPU:

- обучение/инференс AI-моделей с частыми H2D/D2H (host-to-device / device-to-host) копированиями;

- пайплайны со стримингом данных: декодирование/препроцессинг на CPU → батчи на GPU;

- multi-GPU, где часть данных/команд ходит «не там», из-за неудачной привязки к сокету или ограничений P2P.

Когда полоса менее критична

Если данные долго живут в VRAM, а обмен с хостом минимален, то переход с x16 на x8 может почти не проявиться:

- вычислительно плотные ядра;

- батчи помещаются в VRAM и многократно переиспользуются;

- CPU выступает как «оркестратор», а не источник постоянного потока данных.

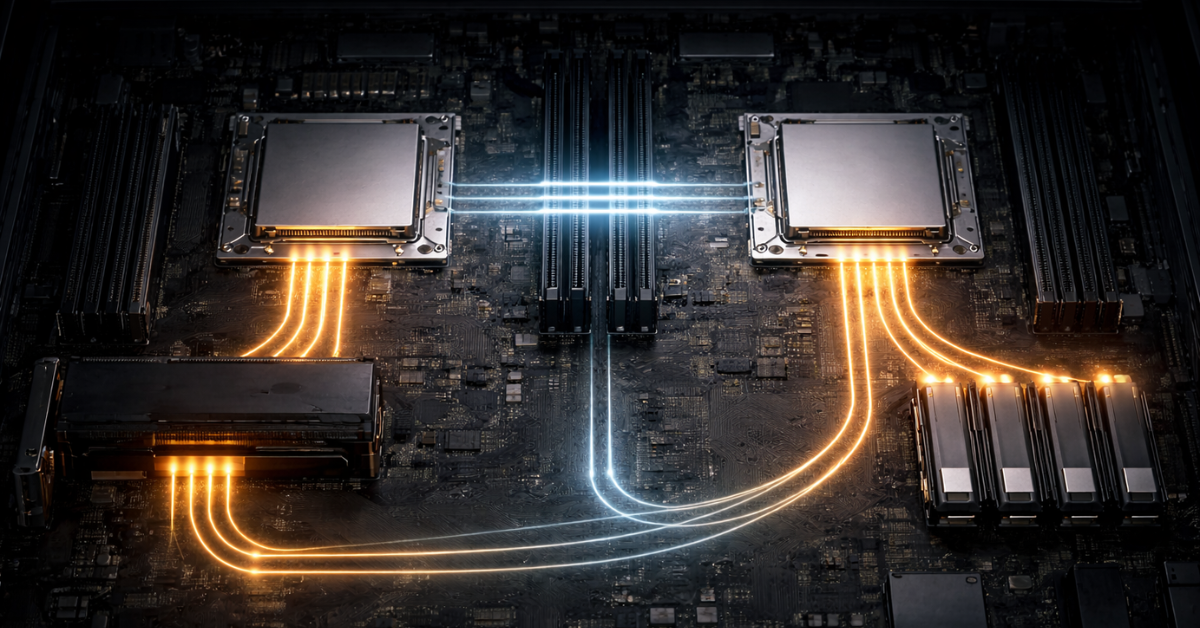

PCIe vs NVLink: корректные ожидания масштабирования multi-GPU

Важно различать:

- CPU↔GPU (обычно PCIe)

- GPU↔GPU (PCIe P2P или NVLink/аналог)

Например, у NVIDIA A100 на странице продукта явно сопоставляются PCIe Gen4: 64 GB/s и NVLink: 600 GB/s (для пары GPU). Это объясняет, почему:

- добавление GPU может масштабировать обучение/распараллеливание «почти линейно» в NVLink-топологиях,

- но при неудачной PCIe/NUMA-топологии вы можете упереться в узкое место при загрузке данных, синхронизациях или пайплайнах без достаточной локальности.

Как читать спецификацию GPU

Смотрите в datasheet/странице продукта:

- PCIe Gen (4/5) и поддерживаемая ширина (x16 или x8);

- наличие NVLink/другого interconnect (если важна связность GPU↔GPU);

- требования к BAR/адресному пространству (важно для BIOS-настроек, про которые будет информация ниже).

Почему PCIe критичен для NVMe: x4, очереди, параллелизм и «сколько дисков можно повесить без сюрпризов»

NVMe — это протокол (спецификация, которая описывает работу с энергонезависимой памятью и очередями команд), а PCIe — интерфейс (транспорт, по которому эти команды/данные ездят). Это формализовано в спецификациях NVM Express по NVMe over PCIe.

Практическая база:

- один NVMe-диск почти всегда подключается как PCIe x4;

- значит, 4 NVMe = 16 линий, 8 NVMe = 32 линии, 16 NVMe = 64 линии — и это только «идеальная математика», без учёта NIC/GPU/контроллеров.

Почему NVMe в реальности может быть медленнее ожиданий, даже если «линий хватает»:

- PCH/аплинк: диски через чипсет делят общий канал к CPU;

- свитч/аплинк: много портов "вниз" (к устройствам), но узкий аплинк "вверх" (к CPU) (оверсабскрипшен);

- термика: Gen5-NVMe легко упирается в охлаждение и уходит в троттлинг;

- очереди/параллелизм: один поток/одна очередь редко раскрывает массив NVMe, а NUMA-удалённость добавляет задержек (латентность).

Топология в двухсокетных серверах: NUMA, “дальний” PCIe и цена межсокетного перехода

В двухсокетной системе устройства обычно «закреплены» за конкретным CPU: часть слотов/райзеров висит на сокете 1, часть — на сокете 2. Если процесс на CPU1 активно читает данные с NVMe, который подключён к CPU2, то данные идут через межсокетный интерконнект (UPI/Infinity Fabric), что добавляет:

- дополнительную латентность,

- непредсказуемость полосы под нагрузкой,

- зависимость результатов от привязки процесса/IRQ.

Принцип локальности:

- держите источник данных и потребителя максимально близко: NVMe ↔ GPU ↔ CPU в пределах одного сокета, если это ваш критичный путь.

Симптомы NUMA-ошибок:

- разные результаты бенчмарков при запуске на разных сокетах/NUMA-нодах;

- «плавающий» throughput без очевидной причины;

- резкая деградация при добавлении второго GPU/второй корзины NVMe (когда нагрузка начинает ездить «через мост»).

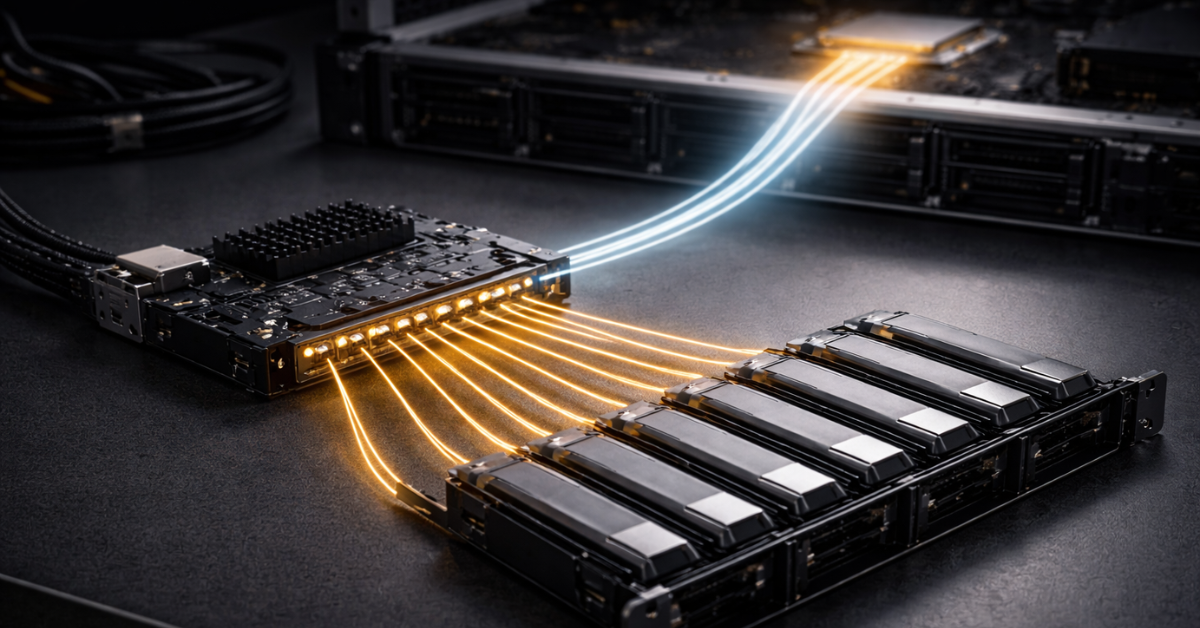

PCIe switch / retimer / riser: когда они спасают, а когда создают bottleneck

Зачем ставят PCIe-свитчи

PCIe-свитч расширяет число downstream-портов: это основа плотных NVMe-бекплейнов, а иногда и GPU-боксов. Но свитч не отменяет физику: у него есть аплинк к CPU/корневому комплексу.

Broadcom (PLX) — типичный поставщик таких решений; семейство PEX88000 — распространённый пример серверных PCIe-switch’ей.

Oversubscription «по-простому»

Это ситуация, когда суммарная потенциальная полоса вниз (к устройствам) больше, чем полоса вверх (к CPU). Пример:

- вниз: 16 NVMe × x4 Gen4 (потенциально очень много),

- вверх: один аплинк x16 Gen4.Пока устройства не загружены одновременно — всё выглядит хорошо. Как только нагрузка становится параллельной — начинается «необъяснимая деградация».

“Non-blocking” — что это значит на практике

Часто “non-blocking” относится к внутренней коммутации свитча, но не отменяет ограничений аплинка. Проверять нужно именно соотношение uplink/downlink и то, какие группы портов агрегируются.

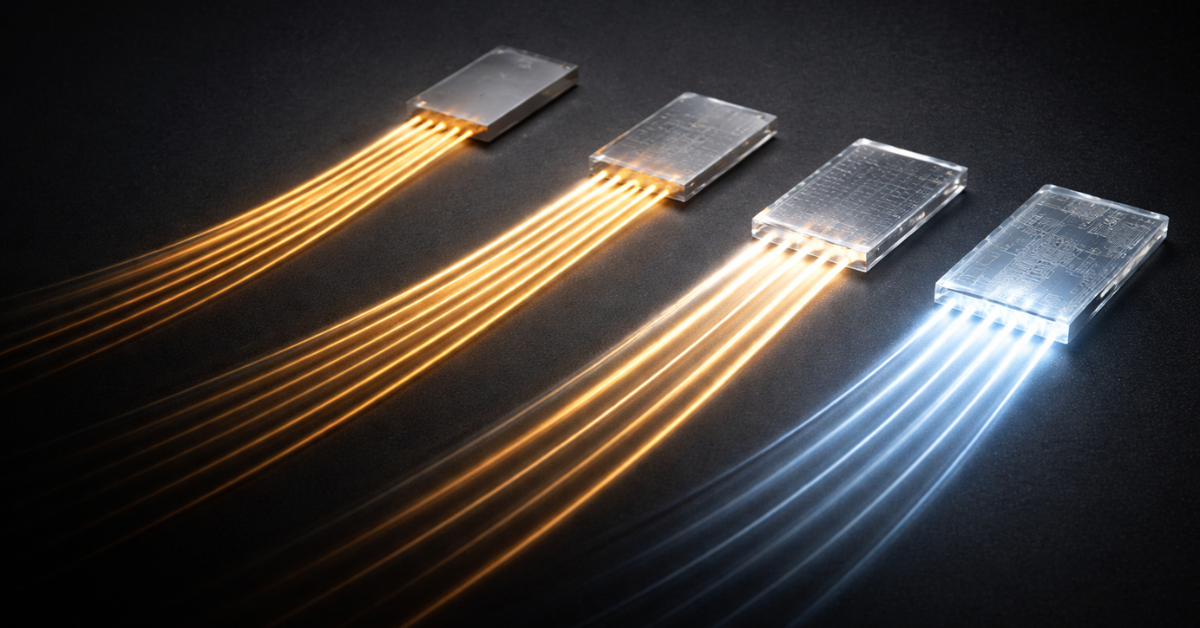

Ретаймеры/райзеры/кабели

Для Gen5/Gen6 качество тракта критично: райзер «вроде такой же» может:

- ухудшить целостность сигнала,

- привести к downtraining (Gen5 → Gen4),

- вызвать нестабильность линка под нагрузкой.

OCP развивает требования к внешней PCIe-связности и ретаймерам как отраслевой тренд (в том числе для дисагрегации NVMe/CXL).

BIOS/прошивки/настройки, которые чаще всего “убивают” линии и устройства

Ниже — чек-лист настроек, которые реально влияют на то, в каком режиме поднимется линк и как будут работать GPU/NVMe/виртуализация:

- PCIe Link Speed (Auto/Gen4/Gen5 принудительно):Auto не всегда лучший — но принудительный Gen5 на плохом тракте может дать нестабильность и откаты.

- Lane bifurcation (x16 → 2×x8 / 4×x4):критично для райзеров и NVMe-адаптеров «на 4 диска».

- Above 4G Decoding:часто необходимо для конфигов с несколькими GPU и большими BAR.

- Resizable BAR:актуально для некоторых сценариев обмена CPU↔GPU (контекстно; зависит от платформы/ПО).

- SR-IOV:для NIC/виртуализации, когда нужно деление устройства на VF.

- ACS/ARI:влияет на изоляцию и маршрутизацию; может мешать P2P, но часто нужен для виртуализации/безопасности.

- IOMMU / VT-d / AMD-Vi:обязательно для passthrough (GPU/NVMe/NIC в ВМ).

- ASPM/энергосбережение:в сервере нередко отключают ради стабильности и предсказуемой латентности.

Практические сценарии расчёта линий: “сколько GPU и NVMe я реально вывезу”

Перед сценариями — простое правило: сначала считайте идеальную математику линий, затем проверяйте топологию (к какому сокету, через что именно, какой аплинк).

Сценарий 1: 2×GPU + 4×NVMe + 200GbE NIC (AI inference / analytics)

Типовая «здоровая» цель без компромиссов:

- 2×GPU: чаще всего 2×x16 (или x8 Gen5 — если осознанно)

- 4×NVMe: 4×x4 = 16 линий

- 200GbE NIC: часто x16 или x8 (зависит от карты)

Итого: порядка 64–80 линий под I/O, плюс запас на контроллеры/доп. NVMe. На платформах с меньшим lane-budget’ом вы быстро начнёте делить слоты или уходить в свитчи.

Сценарий 2: 4×GPU + 8–16×NVMe (плотный AI box / локальный датасет)

Идеальная математика:

- 4×GPU × x16 = 64 линии

- 8×NVMe = 32 линии (или 16×NVMe = 64 линии)

Даже без NIC это уже 96–128 линий. Здесь чаще всего встречаются:

- GPU в x8 вместо x16 (иногда нормально, если Gen5 и вы это планировали),

- NVMe через свитч с оверсабскрипшеном,

- «половина корзины» на другом сокете → NUMA-штраф.

Сценарий 3: NVMe-heavy: 24×NVMe в 2U (storage/cache tier)

24 диска × x4 = 96 линий — «в лоб» почти никогда не разводят напрямую. Почти всегда используется:

- несколько свитчей,

- группировка бекплейна по доменам,

- один или несколько аплинков на CPU(ы),

- и очень важно понимать, где начинается оверсабскрипшен и как он влияет на ваши реальные профили нагрузки.

Примерный бюджет линий и приоритеты

| Устройство | Типичный линк | Критичность к Gen/ширине | Предпочтительное подключение |

| GPU | x16 (иногда x8) | Высокая, если много H2D/D2H, стриминг, tight-coupled пайплайн | CPU-линии, желательно локально к сокету; учитывать P2P/NVLink |

| NVMe SSD | x4 | Средняя/высокая: зависит от параллелизма, профиля I/O, Gen5 чувствителен к термике | CPU-линии для предсказуемости; через свитч — только понимая аплинк/oversubscription |

| NIC 100/200/400G | x8/x16 | Высокая для высоких PPS/low-latency и больших потоков | CPU-линии, локальность к сокету важна |

| HBA/RAID/контроллеры | x8 | Средняя | CPU-линии или PCH (если нагрузка умеренная), но следить за аплинком |

Диагностика: как понять, что вас уже ограничивает PCIe

Симптомы

- GPU работает в x8/x4 вместо x16.

- NVMe не достигает ожидаемых скоростей или график «пилит».

- сильная разница результатов при смене слота/райзера.

- деградация после добавления второй карты/второго бекплейна U.2/EDSFF.

- Gen5 «падает» в Gen4/Gen3 или линк нестабилен.

Симптом → вероятная причина → что сделать

| Симптом | Вероятная причина | Что сделать в первую очередь |

| «x16 физически, но x8 фактически» | дефицит линий, делёж слотов, разводка, настройки BIOS | посмотреть block diagram/мануал платы, проверить bifurcation и занятость соседних слотов |

| NVMe медленнее ожиданий | через PCH/аплинк, свитч-аплинк, термальный троттлинг | переставить на CPU-линии, проверить охлаждение, выяснить uplink/downlink свитча |

| Разные цифры в зависимости от сокета | NUMA-удалённость | привязка процессов/IRQ к нужной NUMA-ноде, перестановка устройств по сокетам |

| Gen5 откатывается в Gen4/Gen3 | сигнал не держится (райзер/ретаймер/кабель/контакты) | заменить райзер/слот, обновить BIOS/firmware, проверить ретаймер-совместимость |

Как выбрать сервер/платформу без ошибки: короткий алгоритм

- Выпишите устройства и требуемые линки:GPU (x16 или допустим x8?), NVMe (сколько × x4), NIC (x8/x16), прочее.

- Определите критичные пути данных:NVMe→GPU? NVMe→CPU? GPU→GPU? NIC→GPU?Это важнее «красивого количества слотов».

- Проверьте lane-budget CPU и block diagram платформы/платы:какие слоты за какой сокет, что идёт через свитч, что через PCH.

- Проверьте поддержку bifurcation/backplane:особенно если NVMe через адаптеры/райзеры «x16 → 4×x4».

- Проверьте ограничения по питанию и термике:Gen5-NVMe и плотные GPU-конфиги часто упираются именно сюда.

- Запланируйте рост:сможете ли добавить +2 NVMe или ещё один NIC без того, чтобы «сломать» ширину/Gen у GPU?

Частые мифы и ошибки

- «Gen важнее ширины всегда» — нет. Важна связка: Gen × ширина × топология × аплинк × NUMA.

- «Если слот x16 — значит будет x16» — не всегда: слот может быть x16 физически, но x8 электрически.

- «PCIe-свитч решит всё» — он решает проблему портов, но не отменяет ограничений аплинка и добавляет латентность.

- «В 2-сокетнике всё одинаково» — нет: NUMA и межсокетный трафик легко превращают «те же линии» в другие задержки и полосу.

Итоги

- PCIe — это поколение + ширина + источник линий (CPU/PCH) + топология.

- «x16 слот» не гарантирует «x16 линк».

- NVMe почти всегда x4 — и много NVMe очень быстро съедают lane-budget.

- CPU-линии обычно важнее PCH-линий из-за латентности и общих аплинков.

- В двухсокетниках локальность (NUMA) может быть важнее «формальной полосы».

- PCIe Gen5/Gen6 требовательны к тракту: райзеры/ретаймеры/длина трасс решают.

- Свитчи помогают по плотности, но требуются расчёты по uplink/downlink и понимание оверсабскрипшена.

- BIOS-настройки (bifurcation, Above 4G, IOMMU/ACS) могут «сломать» ожидаемую конфигурацию.

- Современные платформы отличаются по lane-budget: Xeon до 80 линий PCIe 5.0, EPYC 9004 — 128 линий Gen5.

- Лучший способ не ошибиться — начинать не со «слотов», а с block diagram и критичных путей данных.

Как не ошибиться при заказе/сборке

- Попросите у вендора/интегратора block diagram именно выбранной платы/шасси/райзеров (не «похожей модели»).

- Явно зафиксируйте, какие устройства должны сидеть на CPU-линиях, а где допустим PCH/свитч.

- Уточните, какие слоты/бекплейны относятся к какому сокету (NUMA-план).

- Проверьте, что BIOS поддерживает нужные режимы (bifurcation, Above 4G, IOMMU/VT-d/AMD-Vi).

- Для Gen5 заранее согласуйте райзеры/ретаймеры и охлаждение (иначе «на бумаге Gen5», а по факту Gen4).

Нажимая кнопку «Отправить», я даю согласие на обработку и хранение персональных данных и принимаю соглашение